Calterah Showcases Automotive Radar SoC Cybersecurity and AI-Driven Development Platform at Frankfurt Summits

2026-03-24

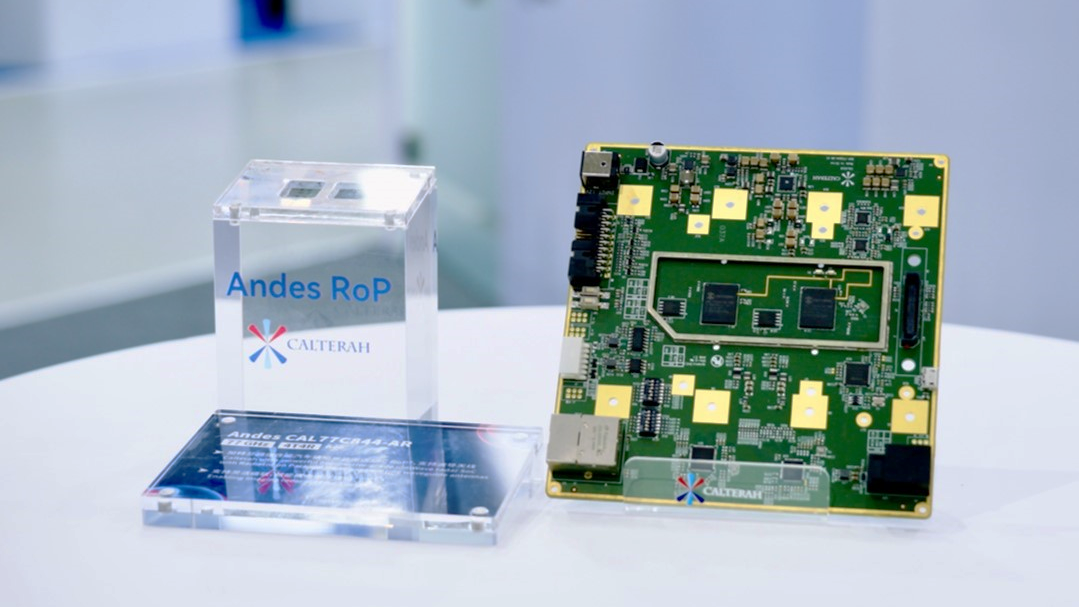

During the recent AutoSec Europe 2026 and SDV & AIDV Europe 2026 summits held concurrently in Frankfurt, Calterah, as a leading provider of automotive radar chips and UWB chips, introduced its technical approach to radar SoC (system-on-chip) cybersecurity and its AI-driven, chip-centric development platform aimed at addressing pain points in automotive radar development.

Founded in 2014, Calterah has established itself as a proven leader in mmWave radar chips and a leading innovator in UWB chips. By the end of 2025, Calterah had achieved collaborations with more than 30 OEMs and cumulative shipments exceeding 20 million chips, being deployed across over 300 vehicle models. The shipment scale not only demonstrates the high reliability of Calterah’s products, but also proves Calterah’s deep expertise in automotive-grade radar chip development and mass production.

As intelligent and software-defined vehicles continue evolving, the need for secure radar semiconductors and more efficient development is increasing. Calterah is building a trusted hardware foundation via chips and a collaborative platform for radar development, advancing the evolution of smart mobility alongside industry partners.

Implementing ISO 21434 in Radar SoCs for Automotive Cybersecurity

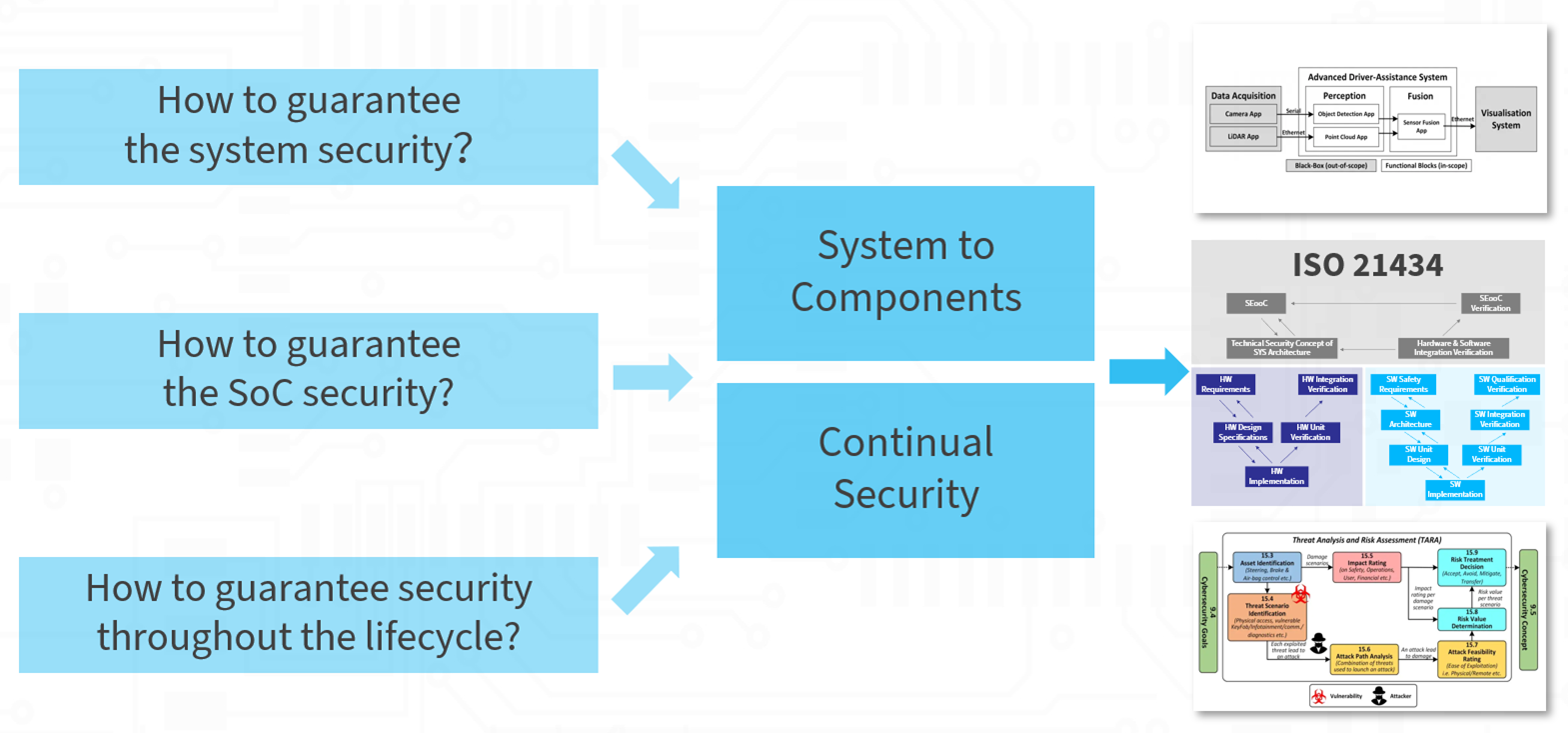

At AutoSec Europe 2026, Yunjie Zhang, Cybersecurity Architect at Calterah, elaborated on Calterah’s practice of implementing the automotive cybersecurity standard ISO 21434 in radar SoC development.

Ever since establishing its Cybersecurity Management System (CSMS) and achieving the ISO 21434 certification in 2023, Calterah has integrated security processes into the full lifecycle of radar chips—from design and development to production. This enables Calterah to support Tier-1s and car OEMs in meeting ISO 21434 and WP.29 R155 requirements, securing automotive radar systems.

Zhang noted that ISO 21434 emphasizes decomposing security requirements from the system level down to the component level. By adopting this "system-to-component" approach, Calterah first identifies critical assets within a vehicle’s electrical and electronic (E/E) architecture—such as configuration data, firmware, keys—before defining chip-level security features. Through Threat Analysis and Risk Assessment (TARA) of radar systems, mandatory features such as secure boot, firmware encryption, key isolation, and cryptographic engines are specified.

Security subsystem requirements are further shaped by performance constraints, system objectives, and international standards, including FIPS 140-2/3, NIST SP 800-90, GM/T 0005, etc. Based on this, Calterah has developed its security IP that meets the compliance needs of global car OEMs and Tier-1s. Plus, Calterah has also established a framework of ongoing vulnerability monitoring and analysis to maintain “continual security”, enabling coordinated responses with customers to emerging threats and helping ensure the reliability and security of intelligent driving decisions.

AI-Driven, Chip-Centric Platform Accelerating Automotive Radar Development

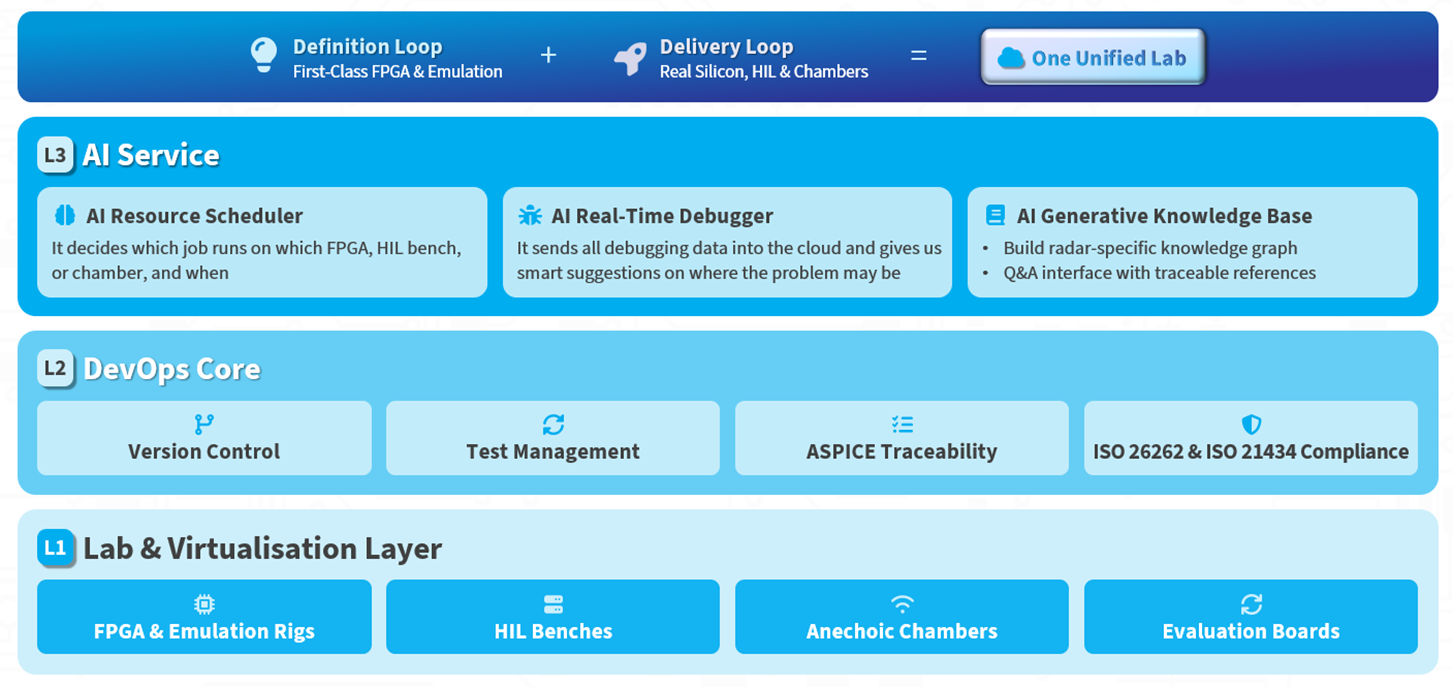

At the SDV & AIDV Europe 2026 summit, Minnan Zheng, Director of Software, introduced an AI-driven, chip-centric DevOps platform, Calterah Radar Cloud Lab, designed for automotive mmWave radar development.

Zheng highlighted in his speech: "The lifecycle of modern automotive radar chips involves two tightly-coupled DevOps loops: the Definition Loop and the Delivery Loop. Traditionally, these loops face four major obstacles: requirement uncertainty, scarce and fragmented hardware resources, time zone and organizational barriers, and debugging difficulties."

*Definition Loop: About 9–12 months; chip design by chip vendors, Tier-1s, and OEMs

*Delivery Loop: About 18 months; from tape-out to SOP (Start of Production).

Calterah Radar Cloud Lab aims to address these challenges with its three-layer design: a lab virtualization layer that registers physical assets (FPGA, HIL benches, evaluation boards, etc.) for unified scheduling and remote access; a DevOps Core layer that manages version control, tests, ASPICE traceability, etc.; an AI service layer consisting of a resource scheduler, a real-time debugger, and a generative knowledge base accessible through natural-language queries.

As introduced by Zheng, the platform can accelerate radar design verification and empower global collaboration. Car OEMs and Tier-1 suppliers can verify designs in cloud-based FPGA environments in advance before physical silicon is available, while AI tools convert requirements into executable test scenarios and enable shared use of scarce hardware. Plus, the AI scheduler coordinates distributed resources to reduce device idle time and shorten engineering queues. Supported by the AI knowledge base, the AI debugger enables highly-efficient cross-time-zone debugging, thus accelerating delivery.

The next phase of development for the platform will focus on expanding virtualization capabilities, integrating partner engineering toolchains, and strengthening AI-based analysis. “We’re looking for European Tier-1s and OEMs to jointly develop a radar cloud laboratory that aligns with local engineering practices and fulfills data-protection requirements,” Zheng said.